レイアウトはPCB設計の重要な部分であり、PCB設計全体の中で最も時間のかかる部分でもあります。エンジニアは、面取りルール、3Wルールなどのいくつかの基本的なルールに従う必要があります。

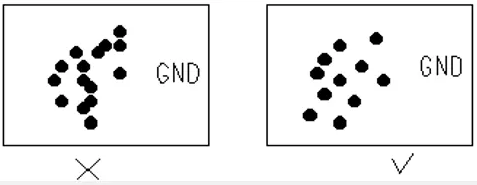

接地回路の規則

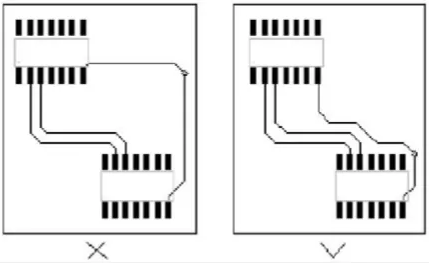

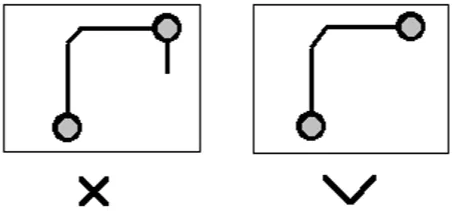

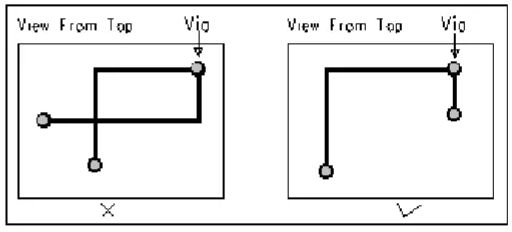

最小ループルールは、信号線とそのループによって形成されるリング領域をできるだけ小さくすることです。リング面積が小さいほど、外部放射が少なくなり、外部から受ける干渉が小さくなります。

この規則によれば、グランドプレーンのスロットリングによって引き起こされる問題を防ぐために、グランドプレーンのセグメンテーションではグランドプレーンと重要な信号線の分布を考慮する必要があります。

二層基板の設計では、電源に十分なスペースを残す場合は、左側の部分を基準接地で埋め、両面信号を効果的に接続するために必要な接地交差穴をいくつか追加する必要があります。一部の重要な信号は、可能な限りアース線で絶縁する必要があります。一部の高周波設計では、グランドプレーン信号回路に特別な配慮を払う必要があります。多層基板の使用をお勧めします

対応する接地回路のルールは、実際には信号のループ領域を最小化することです。これは、クロック信号や同期信号などのいくつかの重要な信号でよく見られます。

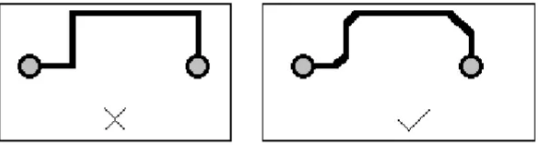

いくつかの特に重要で高周波の信号については、銅シャフトケーブルのシールド構造の設計を検討する必要があります。つまり、アース線を使用してライン、左右を分離し、シールドアースを効果的に組み合わせる方法を検討する必要があります。実際の接地面を考慮する必要があります。

クロストークとは、主に並列ライン間の分布容量とインダクタンスに起因する、PCB上の異なるネットワーク間の長い並列配線によって引き起こされる相互干渉を指します。クロストークを克服するための主な対策は次のとおりです。

The direction control rule of routing, that is, the routing direction of adjacent layers is orthogonal structure. Different signal lines should be avoided to go in the same direction in the adjacent layers to reduce unnecessary inter layer interference; when this situation is difficult to avoid due to board structure constraints (such as some back boards), especially when the signal rate is high, it should be considered to isolate the wiring layers with the ground plane and isolate the signal lines with the land signal lines.

Generally, floating wiring at one end is not allowed(Dangling Line),It is mainly to avoid "antenna effect" and reduce unnecessary interference radiation and acceptance, otherwise it may bring unpredictable results.

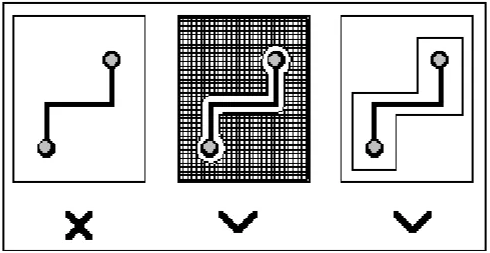

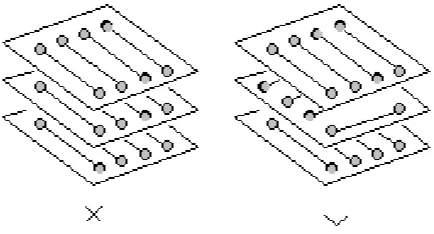

信号線が異なる層間で自己ループを形成するのを防ぎます。この種の問題は、多層プレートの設計で発生しやすく、セルフループが放射干渉を引き起こします。

デバイスのデカップリングルール

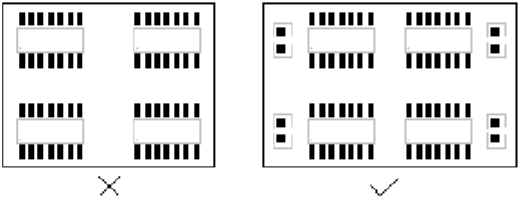

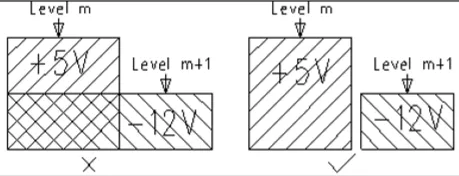

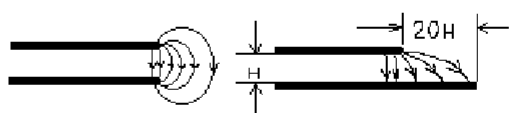

電力層と層の間の電界は可変であるため、電磁干渉がプレートの端から放射されます。これはエッジ効果と呼ばれます。

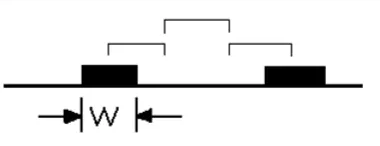

解決策は、電力層を縮小して、電界がグランドプレーンの範囲内でのみ伝導されるようにすることです。H(電源とアース間の誘電体の厚さ)を単位として、電界が20時間インデントされている場合、電界の70%をグランドプレーンのエッジに制限でき、98%の電界は100時間以内に制限されます。