日常生活の中で、私たちは毎日携帯電話、パソコン、ハイビジョンテレビに接触しています。それらの核心はPCBで、高速データ伝送を実現するために、PCBの生産はインピーダンスマッチングから離れられません。

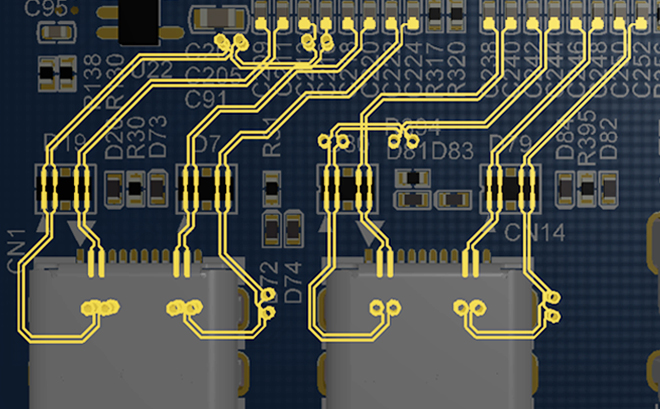

例えば、携帯電話のUSBインタフェースでは、双方向のデータを同期して転送することができ、速度が速く、コストが低く、最も一般的な2つのタイプはType-A、Type-B、Type-Cです。

USBプロトコル定義において(D+、D-)、(TX+、TX-)、(RX+、RX-)差分信号線はデジタル信号を伝送し、伝送信号の安定を保証し、有効外相殺界のコモンモード幹渉を効果的に相殺し、EMIを抑製するために、PCB配線板は差分信号の配線規則に厳格に従わなければなりません。

iPCB(株)は下記注意事項をまとめました。

1.部品間はレイアウト時にできるだけ近く、デバイス間の距離を短くして差分線を最短にし、できるだけ穴をあけないようにします。

2.引き廻しは平行対称である必要があり、90°で角線を引き、45°または弧形で引き廻してはならず、線間隔はできるだけ2 W以内に製御します。

3.直列抵抗容量の場合、抵抗容量は上下または左右に揃えて配置されます。

4.差分線はできるだけ等長線、等距離を歩き、時係列偏差とコモンモード幹渉を避けます。

5.ピン分布、ビア、および引き廻し空間などの要素が存在するため、差分線長が不整合になりやすいが、線長が不整合になると、タイミングがずれ、コモンモード幹渉も導入され、信号品質を低下させます。そのため、対応するのは差分対不整合の状況を補償し、その線長を整合させ、長さ差は通常5 mil以内に製御され、補償原則はどこに長さの差が出てどこを補償します。

工場で使用されているインピーダンス計算はPolar Si 9000で、パラメータは以下のとおりです。

H 1:媒体厚さ(インピーダンス線から参照層までの厚さ)

Er 1:板材の誘電率4.2-4.6(PPは4.2で計算し、Coerは4.5で計算する)

W 1:設計線幅

W 2:上線幅=設計線幅マイナス0.5 mil

S 1:2本の線の間隔

T 1:銅厚、通常1 oz(1.4 mil)で計算

C 1:基材面のソルダーマスク厚さ

C 2:銅箔面のソルダーマスク厚さ

C 3:基材面のソルダーマスク厚さ

CEr:ソルダーマスクの誘電率3.5

(株)iPCBはPCB・PCBAの設計、製造販売及びこれらの付随業務の電子相関事業を手掛けています。弊社の詳細はリンク:https://www.ipcb.jp/ 或いはhttps://www.ipcb.com/jpをご覧ください。