1.はじめに

低消費電力の単一節リチウムイオン電池保護回路を設計し、この保護回路はリチウムイオン電池に過充電、過放電、放電過流保護を提供するだけでなく、充電異常保護、ゼロボルト電池充電禁止などの機能を提供します。1.0μmのダブルウェルCMOSプロセスで実現します。

2.リチウム電池保護ICの機能原理分析

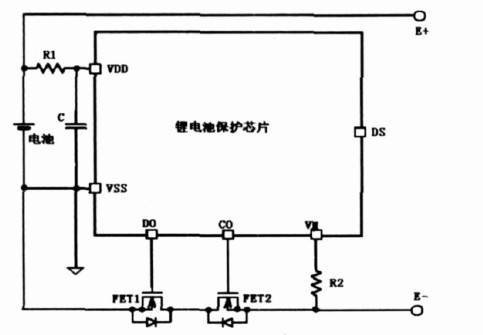

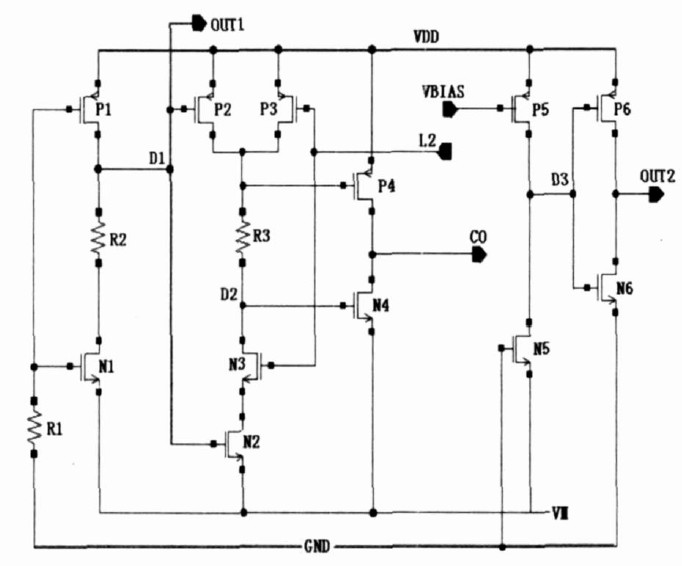

リチウム電池保護回路の原理図を図1に示すように、E+とE−エンドの間に充電器または負荷を加えます。回路の動作原理は次のとおりです。

図1リチウム電池保護原理図

正常状態:電池電圧が過放電検出電圧以上で過充電検出電圧以下、VM端子の電圧が充電器検出電圧以上で過電流検出電圧以下の場合、充電制御用FET 2と放電制御用FET 1の両方がオンになります。

このとき、自由な充電と放電を行うことができます。この状態を正常状態といいます。

過充電保護:充電中、電池電圧が過充電検出電圧より高く、かつこの状態が過充電検出遅延時間まで継続した後、制御回路はローレベルを出力し、充電制御用FET 2をオフにし、充電を禁止します。

放電中、電池電圧が過放電検出電圧より低く、かつこの状態が過放電検出遅延時間まで継続した後、制御回路は低レベルを出力し、放電制御用FET 1をオフにし、放電を禁止します。

過電流保護:過電流保護は過電流保護、二次過電流保護、短絡保護を含み、放電電流が大きすぎ、VM端電圧が上昇し、過電流検出電圧を超え、かつこの状態の持続時間が過電流検出遅延時間を超えた後、制御回路はローレベルを出力し、放電制御用FET 1をオフにし、放電禁止します。放電中、VM端電圧は導通状態にある2つのFET上の電圧降下です(図1参照)。すなわちVVM=I×2RFET.式中、IはFETを通過する電流、すなわち放電電流で、RFETはFETのオン抵抗です。

充電異常保護:電池が充電中に電流が大きすぎてVM端電圧を低下させ、ある設定値より低く、かつこの状態が過充電検出遅延時間以上続くと、制御回路は充電制御用FET 2をオフにし、充電を停止します。VM端電圧が再び設定値以上に上昇すると、充電制御用FET 1が開き、充電保護異常が解除されます。

ゼロボルト電池の充電禁止:電池は長時間放置する場合、自身の放電によって電池電圧が低下し、さらにゼロボルトになり、一部のリチウム電池はその特性の原因で完全に放電された後、再充電に適しません。バッテリ電圧がある設定値を下回ると、充電制御用FET 2のゲートは低電位に固定され、充電が禁止されます。バッテリ自体の電圧がゼロボルトバッテリ禁止充電電圧以上の場合にのみ、充電が許可されます。

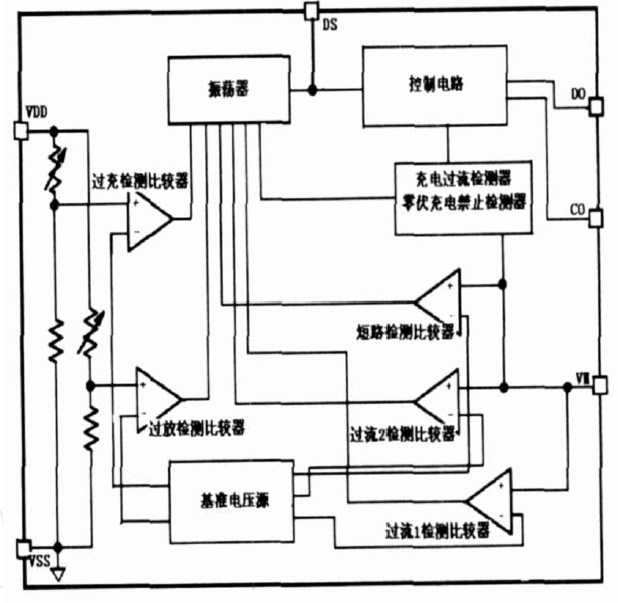

図2に示すように、リチウム電池保護回路は主に基準源、コンパレータ、論理制御回路及びいくつかの追加機能ブロックから構成されています。コンパレータの検出に使用される基準電圧は、チップ要件を満たすために高精度で低消費電力でなければならず、電源電圧が2.2 Vまで低下したときに正常に動作することができる基準ソース回路を介して提供されます。

図2リチウム電池保護回路の内部構成

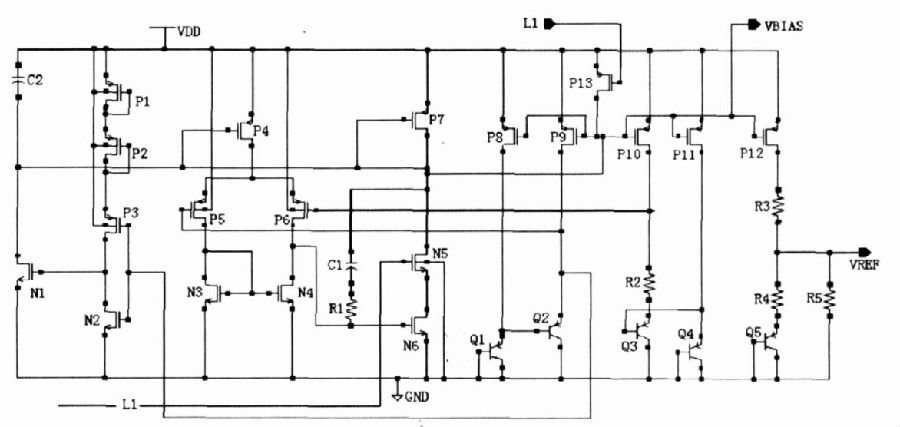

図3は、この要件を満たすバンドギャップ基準ソースです。この回路では、P 4、P 5、P 6、P 7、N 3、N 4、N 6は基準源としてのフィードバックとして2段のキャリアを構成し、キャリアのバイアス電圧は基準源によって提供され、回路とレイアウトを簡略化するとともに、追加の消費電力を削減します。MOS管の寸法を調節することにより、キャリアに高い利得、低い不調電圧を持たせる。基準ソースは段接続ダイオードの形式を採用し、Q 1、Q 2発光領域の面積は等しく、Q 3、Q 4発光領域の面積は等しく、消費電力を減らすために、Q 3の面積をQ 2の2倍とします。段連ダイオード形式は、出力基準電圧の精度に対するキャリアの不調の影響を効果的に低減することができます。

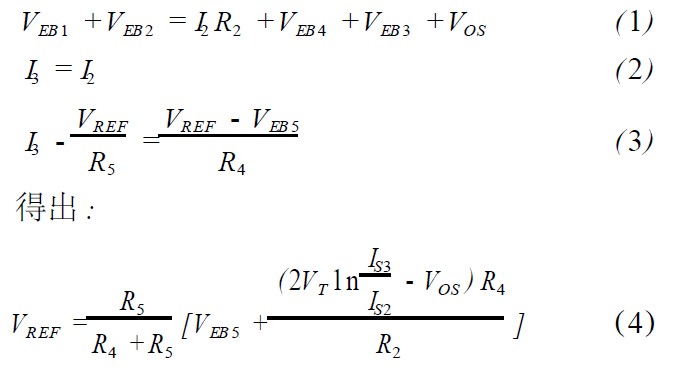

保護回路に用いられる検出電圧は一般的に低く、例えば過電流検出電圧は0.15 V程度、2段過電流検出電圧は0.6 V程度であるが、一般的なバンドギャップ基準回路は1.2 V程度の電圧しか出力できません。抵抗R 5の導入は出力基準電圧を再分圧することでこの問題を解決することです。出力基準電圧の計算式を以下に示します。

図3基準ソース回路構成

式(4)から、2 ln(IS 3/IS 2)VTはln(IS 3/IS 2)VTに対して不調電圧VOSの影響を受けることが明らかに減少し、すなわち段連ダイオードの採用は基準電圧に対してキャリア不調の影響を受けることが減少しました。

式中に因子R 5/(R 4+R 5)が発生し、R 4、R 5の抵抗値を調整することにより、1.2 V未満の基準電圧を得ることができます。

図1において、N 1、N 2、P 1、P 2、P 3、C 1は起動回路として、能動抵抗P 1、P 2は限流作用を果します。N 5、P 13はスイッチング管であり、保護回路がスリープ状態にある場合、回路は動作を停止し、消費電力を低下させなければなりません。この場合、内部制御回路によってL 1を低電位にし、P 13管をオンにし、バイアス点VB IASを高電位に上昇させ、P 4、P 7、P 8、P 9、P 10、P 11、P 12管をオフにし、N 5管をオフにし、P 13、N 6で形成された分岐路を切断し、この回路は動作を停止し、電流はほとんどゼロになります。シミュレーションにより、基準回路は2.2 V電圧で正常に動作することができます。

以下に、充電異常検出機能、ゼロボルト電池充電禁止機能を含むリチウム電池保護ICの追加機能を紹介します。図4をご参考ください。

図4の付加機能回路構成

リチウム電池を充電器に接続して充電すると、VM端は充電器の負端に相当し(図1参照)、1つの-4 V程度のパルス電圧を発生し、N 1管は瞬間的に導通し、同時にOUT 1端も-4 Vのパルス電圧を発生し、論理回路がOUTI端の負パルス電圧を監視した後、論理制御によってL 2を高電位にし、N 3管を導通させ、P 1管のゲート接地のため、VDDがP 1管の閾値電圧より大きい場合、P 1管は導通し、D 1点は高電位、N 2管は導通、D 2点は低電位、P 4管は導通、COは高電位、充電制御用FET 2は開放し、充電を許可し、すなわち充電器検出が完了しました。

リチウム電池が自己放電により自己電圧がPMOS管閾値以下に低下した場合、P 1管がオフ、D 1が低電位、N 2管がオフ、ノードD 2がVM端電圧に低下できず、P 4管がオフ、CO端が低電位、充電制御用FET 2がオフ、充電禁止、すなわちゼロボルト電池充電禁止機能です。充電中、VM端子電位は-I×2 RFET(図1参照)、Iは充電電流、RFETはFETオン抵抗です。電流が大きすぎてVM端電位を負のNMOS閾値以下に低下させると、N 5管が導通し、D 3電位が低下し、P 6管が導通し、出力OUT 2が高電位となり、この状態が一定期間継続した後、制御ロジックはこの状態が有効であると判断し、L 2を低電位、N 3管が遮断し、P 3管が導通し、D 2を高電位、CO端を低電位、充電制御用FET 2が遮断し、充電が停止し、すなわち充電異常検出機能となります。

3.シミュレーションタイミングチャート

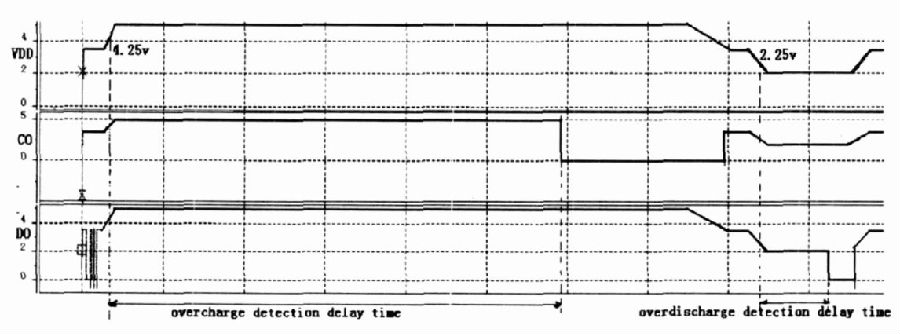

図5は過充電と過放電検出のHSPICEシミュレーションシーケンス図で、コンパレータが電池過充電を検出した場合、ここで過充電検出点は4.25 Vで、この状態保持時間は過充電検出遅延時間に達し、ここでは約1.2秒であり、CO出力はローレベルで、充電用FET 2をオフにし、充電を停止することがわかります。電池の過放電が検出されると、ここでの過放電検出点は2.25 Vで、この状態保持時間は過放電検出遅延時間約150ミリ秒に達し、DOはローレベルを出力し、放電用FET 1をオフし、放電を停止します。放電過電流検出などの他の機能は、HSP ICEシミュレーションを通じて完全に要件に合致しており、ここでは一つ一つ記載されていません。

図5過充電と過放電検出シミュレーションタイミングチャート

4.結論

設計された単一節リチウム電池保護ICは正常動作状態で消費電流が3.3 uA、休眠状態では0.15 uA、過充電検出精度は±25 mVで、-40℃ ~ 85℃の温度で動作でき、製品の性能は完全に要求に合っています。

(株)iPCBはPCB&PCBAの設計、製造販売及びこれらの付随業務の電子相関事業を手掛けています。弊社の詳細はリンク:https://www.ipcb.jp/ 或いはhttps://www.ipcb.com/jp をご覧ください。