USBは高速、双方向、同期伝送、安価、使いやすいホットスワップ可能なシリアルインタフェースです。データ伝送が速く、インタフェースが便利で、ホットスワップをサポートするなどの利点により、USBデバイスが広く応用されている。現在、市場ではUSB 2.0をインタフェースとする製品が多いが、多くのハードウェア初心者はUSBアプリケーションに多くの悩みを抱えており、PCBの組み立てが完了するとUSBインタフェースに通信が不安定になったり通信ができなかったり、原理図や溶接をチェックしても問題がないことが多い。この時はPCBの設計が不合理であることを疑う必要があるかもしれない。USB 2.0データ転送要件を満たすPCBを描画することは、製品の性能と信頼性に極めて重要な役割を果たしています。

USBプロトコルは、2本の差動信号線(D+、D-)によるデジタル信号の伝送を定義し、USBデバイスの動作を安定させるためには、差動信号の規則に厳格に従って配線をレイアウトしなければならない。筆者の長年のUSB関連製品の設計とデバッグの経験に基づいて、以下の注意点をまとめた。

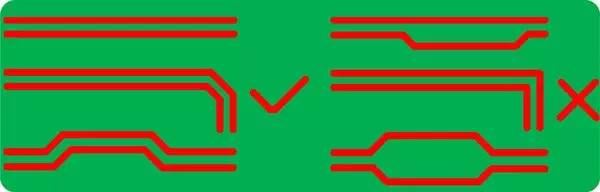

1.素子レイアウトの際、できるだけ差分線路を短くし、差分線路の引き廻し距離を短縮する(√は合理的な方法で、×不合理な方式)。

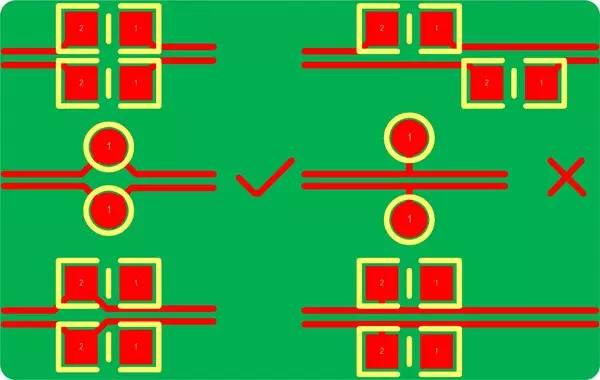

2.差分線を優先的に描画し、1対の差分線の上でできるだけ2対のビア(ビアは線路の寄生インダクタンスを増加させ、それによって線路の信号完全性に影響を与える)を超えないようにし、対称的に配置する必要がある(√は合理的な方法で、×不合理な方式)。

図1

3.対称平行走査線、これにより2本の線が緊密に結合し、90°走査線を避けることができ、円弧または45°はいずれも比較的に良い走査線方式(√は合理的な方式で、×不合理な方式)。

図2

4.差分直列抵抗容量、試験点、上下引張抵抗の配置(√は合理的な方式で、×不合理な方式)。

図3

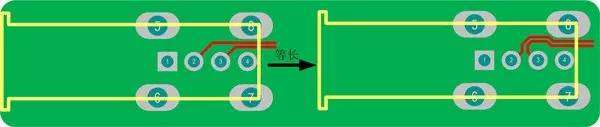

5.ピン分布、ビアリング、及び引き廻し空間などの要素の存在により差分線長が不整合になりやすいが、線長が不整合になると、タイミングがずれ、コモンモード干渉も導入され、信号品質を低下させる。そのため、相応するのは差分対不整合の情況に対して補償をして、その線長を整合させて、長さ差は通常5 mil以内に制御して、補償の原則はどこに長さ差補償のどこが現れるのですか。

図4

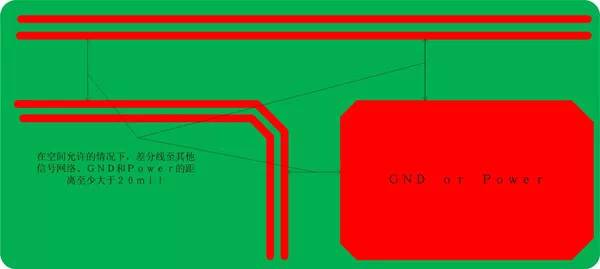

6.クロストークを低減するために、空間的に許容されている場合、他の信号ネットワーク及び地間差動線の間隔は少なくとも20 mil(20 milは経験値)であり、覆地と差動線の距離が近すぎると差動線のインピーダンスに影響を与える。

図5

7.USBの出力電流は500 mAであり、VBUS及びGNDの線幅に注意する必要があり、採用された1 Ozの銅箔の場合、線幅は20 milより大きくてもキャリアの要求を満たすことができ、もちろん線幅が広いほど電源の完全性は良い。

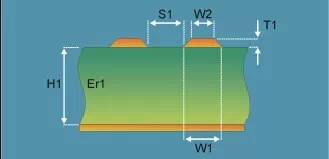

一般的なUSBデバイスの差動線信号線幅及び線ピッチは、基板全体の信号線幅及び線ピッチと一致すればよい。しかし、USBデバイスの動作速度が480 Mbits/sである場合、上記の点だけでは不十分であり、差分信号に対してインピーダンス制御を行う必要があり、差分信号線のインピーダンスを制御することは高速デジタル信号の完全性にとって非常に重要である。差分インピーダンスは差分信号のアイダイヤル、信号帯域幅、信号ジッタ、信号線上の干渉電圧に影響するからである。差動線インピーダンスは一般的に90(±10%)オームに制御される(具体的な値はチップマニュアル指導を参照)、差動線インピーダンスは線幅W 1、W 2、T 1に反比例し、誘電率Er 1に反比例し、線ピッチS 1に比例し、基準層の距離H 1に比例し、下図のように差動線の断面図である。

図6

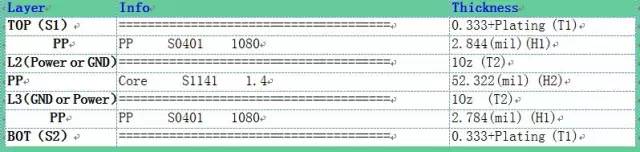

下図は4層基板の参照積層であり、その中の中間2層は参照層であり、参照層は通常GNDまたはPowerであり、差分線に対応する参照層は完全でなければならず、分割されてはならず、そうしないと差分線インピーダンスが不連続になる。図2を用いて4層板を積層設計すると、通常、設計時差分線は4.5 milの線幅と5.5 milの線間隔を用いて差分インピーダンス90Ωを満たすことができる。しかし、4.5 mil線幅と5.5 mil線間隔は私たちの理論設計値にすぎず、最終回路基板工場は要求されたインピーダンス値に基づいて生産の実際の状況と板材を結合して線幅線間隔と参照層までの距離を適切に調整することができる。

図7

以上述べた配線規則はUSB 2.0設備に基づいており、USB配線過程において差動線路が短く、密着結合、等長、インピーダンスが一致し、USB電源線の載置能力に注意し、以上の原則を把握してUSB設備の運行は基本的に問題ない。