ガラス基板は、生成AIや高性能コンピューティングの爆発的な需要に押され、半導体パッケージングの次世代コア素材として急速に注目を集めている。従来の有機樹脂基板(主にガラスエポキシ)が長年主流だったが、チップレットアーキテクチャの広がりとともにその限界が明らかになりつつある。シリコン製チップと基板の熱膨張率(CTE)のミスマッチが大型パッケージで深刻な歪みを生み、信頼性低下や歩留まり悪化を招くからだ。ここでガラスが持つCTEの低さ(約3ppm/℃前後でシリコンに極めて近い)が決定的な強みとなる。

Intelが2023年頃から本格的にガラス基板のロードマップを公表して以来、業界全体が動き出した。ガラスコア基板を採用することで、最大240mm角、将来的には500mm角超えのパネルサイズ対応が可能になり、パネルレベルパッケージ(PLP)の生産性が飛躍的に向上する。樹脂基板では大型化するとワーページ(反り)が避けられないが、ガラスの高い剛性と平坦性がこれを劇的に抑制する。平坦度が高いため、再配線層(RDL)の微細化も進みやすく、配線幅/間隔(L/S)を2〜5μmレベルまで縮小、貫通ガラスビア(TGV)のピッチも40〜150μm程度で高密度実装を実現できる見通しだ。これにより同一パッケージ内に搭載できるチップレット数が大幅に増え、GPUとHBMの混載や多コアAIアクセラレータのスケールアップが現実的になる。

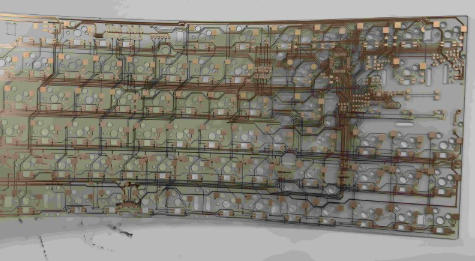

図 ガラス基板

電気的特性でもガラスは優位だ。誘電率(Dk)と損失正接(Df)が樹脂より低く、信号の伝送損失が抑えられるため、高周波・高速シグナルの劣化が少ない。生成AI向けの数百Tbps級帯域幅を必要とするインタコネクトでは、この低損失特性が直接性能に寄与する。TGV加工技術もここ数年で飛躍的に進化しており、CO2レーザーや超短パルス深紫外レーザーによる直接加工でアスペクト比20以上の微細貫通穴をクラックなく形成できるようになった。AGCや日本電気硝子(NEG)のようなガラスメーカーがEN-A1などの専用組成を開発し、化学エッチングを最小限に抑えた環境負荷の低いプロセスも確立されつつある。

一方で課題も少なくない。ガラス特有の脆さによる「背割れ」やハンドリング時の破損リスクは依然として残り、量産ラインでの歩留まり確保が最大のハードルだ。TOPPANやDNPのような印刷大手が510×515mmサイズのガラスコアをデモし、厚み0.4〜1mmでTGV仕様を揃え、2028年頃の事業化を公言しているが、コストはまだ有機基板の数倍〜十数倍と見積もられている。Intelですら2020年代後半〜2030年初頭の量産移行を計画しており、完全な置き換えではなく、当面はハイエンドAI/データセンター向けに限定される可能性が高い。

それでも中国勢の参入が加速している点は見逃せない。BOEをはじめディスプレイ・PCBメーカーがガラス基板市場に雪崩れ込み、供給過剰と価格競争を呼び込む兆しもある。市場調査では2036年までにガラス関連半導体素材市場が44億ドル規模に成長すると予測されており、年平均成長率14%超という数字が示すように、不可逆的な流れに入ったと言える。

ガラス基板の採用は単なる材料変更ではなく、パッケージ設計思想そのものの転換を意味する。チップレット時代の本格到来とともに、熱・電気・機械特性を同時に最適化できる基板が求められる中、ガラスはその答えの一つとして存在感を増している。シリコンインターポーザーと有機基板の「中間」を埋める存在から、やがて主流へと移行する日が近づいている。