PCBの設計プロセス、電力面又は接地面の分割は、不完全な平面につながります。信号がルーティングされると、その基準面は1つの電源面から別の電源面に交差します。この現象は、信号のクロスセグメンテーションと呼ばれます。

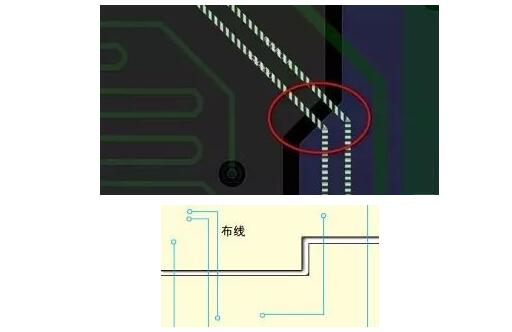

クロスセグメンテーション現象の概略図

高速デジタル信号システムでは、高速信号は基準面をリターンパス、つまりリターンパスとして使用します。参照面が不完全な場合、次の悪影響が発生します。

配線のインピーダンスの不連続性が発生します。

信号間のクロストークは簡単に発生します。

信号間の反射を引き起こします。

電流のループ面積とインダクタンスを増やすと、出力波形が発振しやすくなります。

同時に、宇宙磁場の影響を受けやすいです。

ボード上の他の回路との磁場結合の可能性を高めます。

ループインダクタンスの高周波電圧降下は、コモンモード放射源を形成し、外部ケーブルを介してコモンモード放射を生成します。

したがって、PCB配線はできるだけ平面に近づけ、クロスセグメンテーションを回避する必要があります。これらの条件は、低速信号線で分割を通過する必要がある場合、または電源のグランドプレーンに近づけることができない場合にのみ許可されます。

設計におけるスパンセグメンテーションの処理

PCB設計で避けられないクロスセグメンテーションにどのように対処しますか?この場合、信号の短いリターンパスを提供するためにセグメンテーションを縫う必要があります。一般的な処理方法は、ミシンコンデンサを追加し、ラインをブリッジすることです。

、ステッチコンデンサ

通常、0402または0603パッケージのセラミックコンデンサが信号断面に配置されます。コンデンサの静電容量値は0.01uFまたは0.1uFです。スペースが許せば、そのようなコンデンサをさらにいくつか追加することができます。

同時に、信号線がミシンコンデンサの200milの範囲内にあることを確認し、距離が小さいほど良いことを確認してください。一方、コンデンサの両端のネットワークは、信号が通過する基準面のネットワークに対応します。下の図のコンデンサの両端に接続されているネットワーク、明るい色の2つの異なるネットワークを参照してください。

クロスラインブリッジ

信号層のセグメンテーション全体で信号を「パケットグラウンド」するのが一般的です。そうでない場合は、他のネットワークの信号線が含まれる可能性があります。この「パケットグラウンド」ラインは、できるだけ太くする必要があります。この処理方法については、下図を参照してください。

高速信号配線スキル

多層配線

高速信号配線回路は、通常、高度に統合されており、配線密度が高くなっています。多層基板の使用は、配線だけでなく、干渉を低減するための効果的な手段でもあります。

層数を適切に選択することで、プリント基板のサイズを大幅に縮小し、中間層を最大限に活用してシールドを設定し、近くの接地をより適切に実現し、寄生インダクタンスを効果的に低減し、信号の伝送長を効果的に短縮できます。信号間の相互干渉を大幅に低減します。

リード線の曲がりが少ないほど良い

高速回路のピン間のリードベンドが少ないほど良いです。

高速信号配線回路のリード線は、完全な直線を採用しているため、回す必要があり、45°の破線または円弧で回すことができます。この要件は、低周波回路での鋼箔の固定強度を向上させるためにのみ使用されます。

高速回路では、この要件を満たすことで、高速信号の外部放射と結合を減らし、信号の放射と反射を減らすことができます。

リードが短いほど良い

高速信号配線回路のデバイスピン間のリード線は短いほど良いです。

リード線が長いほど、分布インダクタンスと静電容量が大きくなり、システムの高周波信号の通過に大きな影響を与え、回路の特性インピーダンスも変化して、システムの反射と発振を引き起こします。

層間交代が少ないほど良い

高速回路のピン間のリード層の交代が少ないほど良いです。

いわゆる「リードの層間交代が少ないほど良い」とは、コンポーネント接続のプロセスで使用されるビアが少ないほど良いことを意味します。

ビアは約0.5pfの分布容量をもたらす可能性があり、これにより回路遅延が大幅に増加することが測定されています。ビアの数を減らすと、速度を大幅に向上させることができます。

並列交差干渉に注意してください

高速信号配線では、信号線の密な並列配線によって引き起こされる「相互干渉」に注意を払う必要があります。並列分配が避けられない場合は、並列信号線の反対側に広い領域の「グラウンド」を配置して、干渉を大幅に減らすことができます。

枝や切り株を避ける

高速信号配線は、分岐やスタブを回避する必要があります。

切り株はインピーダンスに大きな影響を及ぼし、信号の反射やオーバーシュートにつながる可能性があるため、設計では切り株や分岐を避ける必要があります。

菊のチェーン配線を使用すると、信号への影響を軽減できます。

信号線は可能な限り内層にある必要があります

高周波信号線は、表面に出たときに大きな電磁放射を発生しやすく、外部の電磁放射や要因による干渉も受けやすいです。

高周波信号線を電源とアース線の間に敷設すると、電源と最下層が電磁波を吸収することにより、発生する放射線が大幅に減少します。