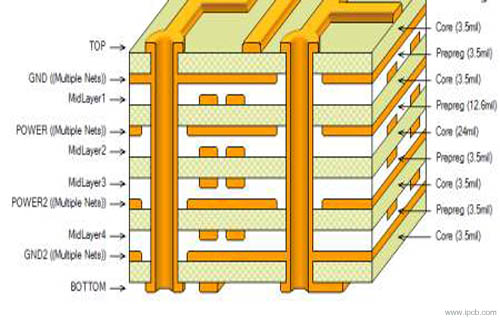

PCBスタックの設計ではどのような問題に注意を払う必要がありますか?ここで、ipcbエンジニアに教えてもらいます。

スタックを設計するときに従うべき2つのルールがあります。

1.各ルーティング層には、隣接する参照層(電源または層)が必要です。

2.結合容量を大きくするために、隣接する主電源層と層の間の距離を維持する必要があります。

説明のために、2枚、4枚、6枚のプライボードの例を挙げましょう。

オプション1

片面PCBと両面PCBのラミネート

2層基板の場合、EMI放射の制御は、主に配線とレイアウトから考慮されます。

単層基板と二重層基板のEMC問題はますます顕著になっています。この現象の主な理由は、信号ループ領域が大きすぎるため、強力な電磁放射が発生するだけでなく、回路が外部干渉の影響を受けやすくなるためです。送電線の電磁両立性を改善するための簡単な方法は、主に強い放射信号と敏感な信号を参照する主要な信号のループ面積を減らすことです。

単層および二重層プレートは通常、10kHz未満の低周波シミュレーション設計で使用されます

1)同じ層の電源が放射状に配置され、ラインの全長がマージされます。

2)電源とアース線は互いに近接している必要があります。アース線は、信号線にできるだけ近いキー信号線の横に配置する必要があります。このようにして、より小さなループ領域が形成され、外部干渉に対する差動モード放射の感度が低下します。

3)2層回路基板の場合、回路基板の反対側の信号線に沿って信号線の近くにアース線を敷設することができ、線はできるだけ広くする必要があります。

オプション2

4層プレートのラミネート

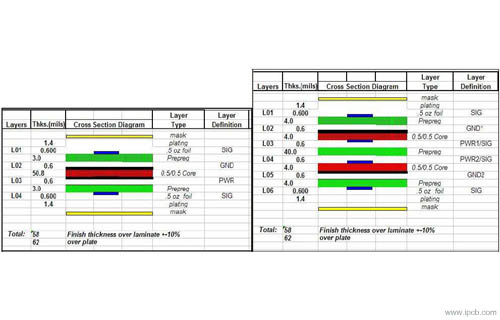

1. SIG-GND(PWR)-PWR(GND)-SIG;

2. GND-SIG(PWR)-SIG(PWR)-GND;

上記の2つのラミネート設計の潜在的な問題は、従来の1.6 mm(62 mil)のプレートの厚さです。層の間隔が非常に大きくなり、インピーダンス、層間結合、およびシールドの制御に役立ちません。特に、電力層間の間隔が大きいと、プレートの静電容量が減少し、ノイズフィルタリングに役立ちません。

このスキームは通常、より多くのオンボードチップの場合に使用されます。このスキームはSiのパフォーマンスを向上させることができますが、EMIのパフォーマンスにはあまり適していません。これは主にルーティングやその他の詳細によって制御されます。

2番目のスキームは通常、ボード上のチップの密度が十分に低く、チップの周囲に十分な領域がある場合に使用されます。このスキームでは、PCBの外層はすべて層であり、中央の2つの層は信号/電力層です。EMI制御の観点から、これは既存の4層PCB構造です。

主な注意:クロストークを避けるために、中央の2つの層の信号層と電力混合層の間の距離を開き、配線方向を垂直にする必要があります。コントロールボードの領域は、20時間のルールを反映するために適切である必要があります。

オプション3

6層プレートのラミネート

チップ密度が高く、クロック周波数が高い設計の場合、6層ボードの設計を検討する必要があります。

1.SIG-GND-SIG-PWR-GND-SIG;

信号層はグラウンド層に隣接しており、パワー層とグラウンド層はペアになっています。各層のインピーダンスは適切に制御でき、2つの層は磁力線を吸収できます。

2.GND-SIG-GND-PWR-SIG-GND;

このスキームは、デバイス密度がそれほど高くない場合にのみ適しています。このスタックには、上部スタックのすべての利点があり、最上層と最下層のグランドプレーンは比較的完全であるため、より優れたシールド層として使用できます。したがって、EMI性能は他の方式よりも優れています。

要約:2番目のスキームと比較して、2番目のスキームのコストは大幅に増加します。したがって、通常、スタックするときに1つのスキームを選択します。