Viaは多層PCBの重要なコンポーネントの1つであり、通常、穴あけのコストはPCB製造コストの30%から40%を占めます。簡単に言えば、PCBのすべての穴はビアと呼ぶことができます。機能の観点から、ビアは2つのカテゴリに分類できます。1つは層間の電気的接続に使用されます。もう1つは、デバイスの固定または位置決めに使用されます。プロセスの観点から、これらのビアは一般に、ブラインドビア、埋め込みビア、スルービアの3つのカテゴリに分類されます。ブラインドビアはプリント回路基板の上面と下面にあり、一定の深さがあります。これらは、サーフェスラインとその下にあるインナーラインを接続するために使用されます。穴の深さは通常、特定の比率(開口部)を超えません。埋め込み穴とは、プリント回路基板の内層にある接続穴のことで、回路基板の表面までは伸びていません。

上記の2種類の穴は、回路基板の内層に配置され、積層前にスルーホール形成プロセスによって完成され、ビアの形成中にいくつかの内層が重なり合う可能性がある。3番目のタイプはスルーホールと呼ばれ、回路基板全体を貫通し、内部相互接続またはコンポーネント取り付け位置決め穴として使用できます。スルーホールはプロセスでの実装が容易でコストが低いため、ほとんどのプリント回路基板は他の2種類のスルーホールの代わりにスルーホールを使用します。下記のビア穴は、特に指定のない限り、ビア穴とみなされます。これは回路基板の表面までは伸びていません。

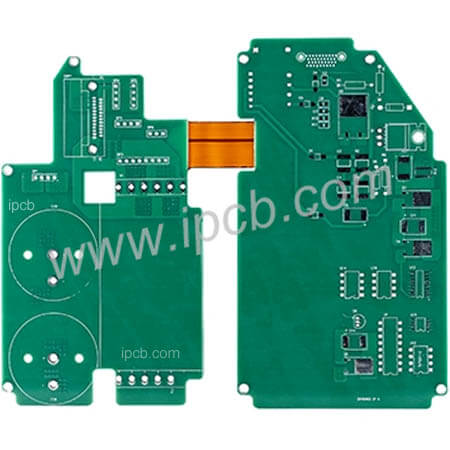

図1 高速プリント基板

設計の観点から、ビアは主に2つの部分で構成され、1つは中央のドリル穴で、もう1つはドリル穴の周囲のパッド領域です。これら2つのパーツのサイズによって、ビアのサイズが決まります。明らかに、高速高密度PCB設計では、設計者は常にビアホールが小さいほど良いことを望んでいるため、ボード上により多くの配線スペースを残すことができます。さらに、ビアホールが小さいほど、それ自体の寄生容量が大きくなります。小さいほど高速回路に適しています。ただし、穴のサイズを小さくするとコストも高くなり、ビアのサイズを無期限に小さくすることはできません。穴あけやメッキなどのプロセス技術によって制限されます。穴が小さいほど、穴あけが多くなります。穴が長くなるほど、中心位置から外れやすくなります。また、穴の深さがドリル穴の直径の6倍を超えると、穴の壁に銅を均一にめっきできるとは限りません。

たとえば、通常の6層PCBボードの厚さ(スルーホールの深さ)が50Milの場合、通常の条件下では、PCBメーカーが提供する最小穴あけ直径は8Milにしか達しません。レーザー穴あけ技術の開発により、穴のサイズはどんどん小さくなります。一般に、直径が6Mils以下のビアはマイクロホールと呼ばれます。マイクロビアは、HDI(高密度相互接続構造)の設計でよく使用されます。Microviaテクノロジーにより、ビアをパッドに直接パンチすることができ(Via-in-pad)、回路性能が大幅に向上し、配線スペースが節約されます。穴の壁に銅を均一にめっきできることを保証することはできません。たとえば、通常の6層PCBボードの厚さ(スルーホールの深さ)が50Milの場合、通常の条件下では、PCBメーカーが提供する最小穴あけ直径は8Milにしか達しません。レーザー穴あけ技術の開発により、穴のサイズはどんどん小さくなります。一般に、直径が6Mils以下のビアはマイクロホールと呼ばれます。マイクロビアは、HDI(高密度相互接続構造)の設計でよく使用されます。Microviaテクノロジーにより、ビアをパッドに直接パンチすることができ(Via-in-pad)、回路性能が大幅に向上し、配線スペースが節約されます。穴の壁に銅を均一にめっきできることを保証することはできません。

ビア基板は、伝送ライン上で不連続なインピーダンスを持つブレークポイントとして表示され、信号の反射を引き起こします。一般に、ビアの等価インピーダンスは伝送ラインの等価インピーダンスよりも約12%低くなります。たとえば、50オームの伝送ラインのインピーダンスは、ビアを通過するときに6オーム減少します(具体的には、絶対的な減少ではなく、ビアのサイズと厚さに関係します)。ただし、ビアの不連続インピーダンスによって引き起こされる反射は実際には非常に小さく、その反射係数は(44-50)/(44 + 50)= 0.06のみです。ビア基板によって引き起こされる問題は、寄生容量と寄生インダクタンスに集中しています。

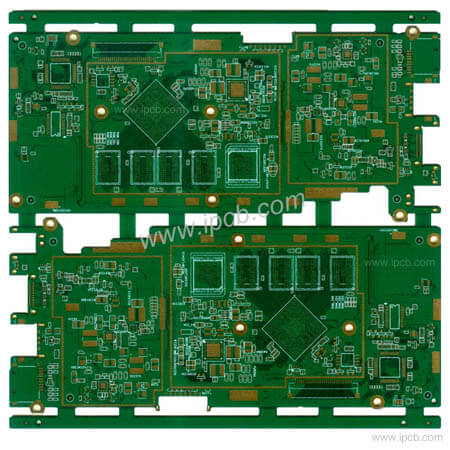

図2 高速プリント基板

第二に、ビア基板の寄生容量とインダクタンスビア自体には寄生浮遊容量があります。ビア基板の接地層のソルダーマスクの直径がD2、ビアパッドの直径がD1、PCBボードの厚さがT、ボード基板の誘電率がεであることがわかっている場合、ビアの寄生容量はおおよそ次のとおりです。C=1.41εTD1/(D2-D1)

回路に対するビアホールの寄生容量の主な影響は、信号の立ち上がり時間を延長し、回路の速度を低下させることです。たとえば、厚さが50MilのPCBボードの場合、ビアパッドの直径が20Mil(穴の直径が10Mil)で、ソルダーマスクの直径が40Milの場合、上記の式を使用することにより、寄生容量はおおよそ次のようになります。C= 1.41x4.4x0.050x0.020 /(0.040-0.020)= 0.31pF

容量のこの部分によって引き起こされる立ち上がり時間の変化は、おおよそ次の公式どおりです。T10-90= 2.2C (Z0 / 2)= 2.2x0.31x(50/2)= 17.05ps

これらの値から、単一のビアの寄生容量によって引き起こされる立ち上がり遅延の影響はあまり明白ではありませんが、ビアをトレースで複数回使用してレイヤを切り替えると、複数のビアが使用されることがわかります。設計は慎重に検討する必要があります。実際の設計では、ビア基板ホールと銅領域(アンチパッド)の間の距離を大きくするか、パッドの直径を小さくすることで、寄生容量を減らすことができます。

寄生容量は、寄生インダクタンスだけでなくビアにも存在します。高速デジタル回路の設計では、ビアの寄生インダクタンスによって引き起こされる害は、寄生容量の影響よりも大きいことがよくあります。その寄生直列インダクタンスは、バイパスコンデンサの寄与を弱め、電力システム全体のフィルタリング効果を弱めます。次の実験式を使用して、ビアの寄生インダクタンスを簡単に計算できます。L= 5.08h [ln(4h / d)+1]

ここで、Lはビア基板のインダクタンス、hはビアの長さ、dは中央の穴の直径です。式から、ビア基板の直径がインダクタンスに与える影響は小さく、ビアの長さがインダクタンスに与える影響が最も大きいことがわかります。上記の例を

引き続き使用すると、ビアのインダクタンスは次のように計算できます。L= 5.08x0.050 [ln(4x0.050 / 0.010)+1] = 1.015nH

信号の立ち上がり時間が1nsの場合、それに相当するインピーダンスはXL =πL/ T10-90 =3.19Ωです。このようなインピーダンスは、高周波電流が流れるときに無視できなくなります。電源層とグランド層を接続するときは、バイパスコンデンサが2つのビアを通過する必要があるため、ビアの寄生インダクタンスが2倍になることに特に注意する必要があります。

図3 高速プリント基板

第三に、ビア基板の使用方法の寄生特性の上記の分析を通して、高速PCB設計では、一見単純なビアが回路設計に大きな悪影響をもたらすことが多いことがわかります。ビアの寄生効果によって引き起こされる悪影響を低減するために、設計で次のことを行うことができます。

1.コストと信号品質の両方を考慮して、適切なサイズのビアサイズを選択します。必要に応じて、さまざまなサイズのビアの使用を検討できます。たとえば、電源ビアまたはグランドビアの場合は、インピーダンスを減らすために大きなサイズを使用することを検討できます。信号トレースの場合は、小さなビアを使用できます。もちろん、ビアのサイズが小さくなると、対応するコストも増加します。

2.上記の2つの式は、より薄いPCBを使用すると、ビアの2つの寄生パラメータを減らすのに有益であると結論付けることができます。

3. PCBボード上の信号トレースの層を変更しないようにします。つまり、不要なビアを使用しないようにします。

4.電源とアースのピンを近くにドリルで開け、ビアとピンの間のリード線をできるだけ短くする必要があります。等価インダクタンスを減らすために、複数のビアを並列に再生することを検討してください。

5.信号に最も近いリターンを提供するために、信号層のビアの近くにいくつかの接地されたビアを配置します。PCBに冗長グランドビアを配置することもできます。

6.高密度の高速PCBボードの場合、マイクロビアの使用を検討できます。