回路基板設計では、信号完全性(SI)の問題が早期に解決されるほど、設計の効率が高くなり、回路基板設計が完了してから端子デバイスが追加されるのを回避することができます。SI設計計画にはツールやリソースが少なくありませんが、信号整合性の核心議題とSI問題を解決するいくつかの方法を模索しています。

1、SI問題の提出

IC出力スイッチ速度の向上に伴い、信号周期にかかわらず、ほとんどの設計で信号完全性の問題が発生しています。過去にSIの問題に遭遇していなくても、回路の動作周波数が高くなるにつれて、今後は必ず信号完全性の問題に遭遇します。

信号完全性の問題は主に信号のオーバーシュートと減衰発振現象を指し、それらは主にIC駆動振幅とホッピング時間の関数である。つまり、配線トポロジ構造が変化しなくても、ウェハ速度が十分に速くなれば、既存の設計は臨界状態にあるか、動作を停止することになる。信号完全性設計が避けられないことを2つの例で説明します。

例の1:通信分野では、最先端の電気通信会社が音声と資料の交換のために高速回路基板(500 MHzより高い)を生産しているが、この場合のコストは特に重要ではないので、できるだけ多層板を採用することができる。このような回路基板は十分な接地を実現し、電源回路を構成しやすくすることができ、必要に応じて大量の離散的な端子デバイスを採用することもできるが、設計は正確でなければならず、臨界状態にあることはできない。

SIとEMCの専門家は配線の前にシミュレーションと計算を行い、その後、回路基板設計は一連の非常に厳格な設計規則に従うことができ、疑問の点では、エンドコネクタデバイスを追加することができ、できるだけ多くのSIセキュリティマージンを得ることができます。回路基板の実際の動作中には、常にいくつかの問題が発生します。そのため、制御可能なインピーダンス端子配線を採用することで、SIの問題を回避することができます。簡単に言えば、超標準設計はSI問題を解決することができます。

例の2:コストの観点から、回路基板は通常4層以内(内部の2層はそれぞれ電源層と接地層)に制限される。これはインピーダンス制御の役割を大きく制限している。また、配線層が少ないとクロストークが激化し、信号線の間隔も最小にしてより多くのプリント線を配置しなければならない。一方、設計エンジニアは、SIの問題を考慮しなければならない最新で最高のCPU、メモリ、ビデオバスの設計を採用しなければなりません。

配線、トポロジ構造、エンドキャップ配管については、CPUメーカーから多くの提案を受けることができますが、これらの設計ガイドは製造プロセスと組み合わせる必要があります。回路基板設計者の仕事は、新規インピーダンス制御や端子デバイスのスペースが小さいため、電気通信設計者の仕事よりも難しいことが大きい。その際には、製品の設計期間を確保しながら、それらの不完全な信号を十分に研究して解決しなければならない。

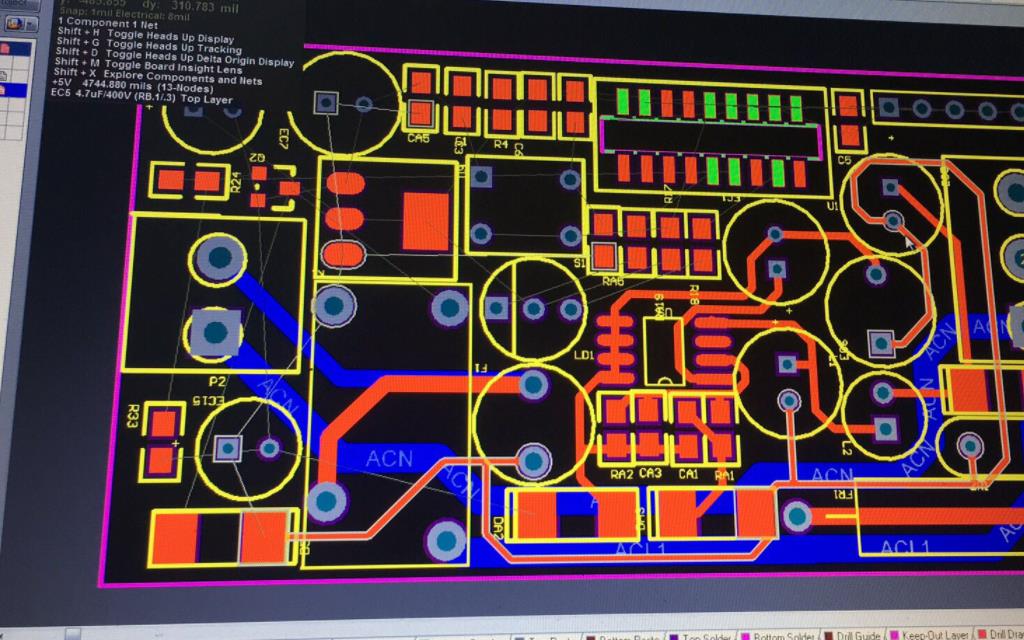

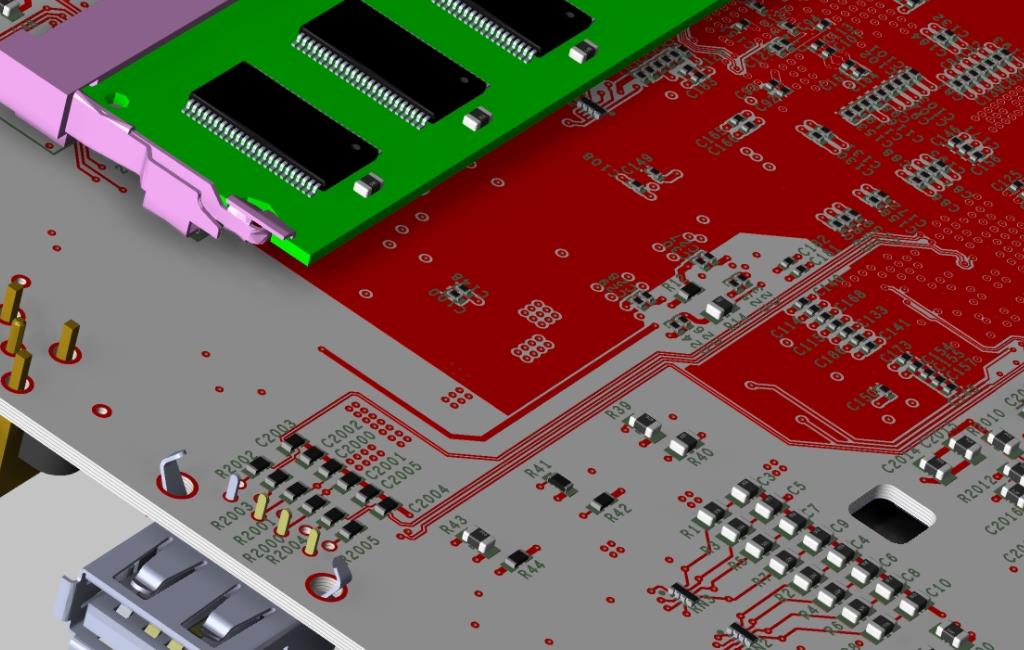

基板設計

次に、基板設計プロセスに共通するSI設計ガイドラインについて説明します。

2、回路基板設計前の準備作業

設計を開始する前に、部品の選択、プロセスの選択、回路基板の生産コスト制御などの作業を指導するために、設計戦略を考えて決定する必要があります。SIについては、設計結果に明らかなSI問題、クロストーク、タイミング問題が発生しないように、事前に調査を行って計画または設計基準を形成しなければならない。一部の設計基準はICメーカーが提供することができますが、ウェハベンダーが提供する基準(または自分で設計する基準)には限界があり、このような基準ではSI要件を満たす回路基板を設計することはできない可能性があります。設計規則が簡単であれば、設計エンジニアも必要ありません。

実際に配線する前に、まず次の問題を解決しなければなりません。多くの場合、これらの問題は設計中(または設計を検討中)の基板に影響を与えます。基板の数が多い場合、この作業は価値があります。

3、回路基板の積層

いくつかのプロジェクトグループはPCB階数の確定に大きな自主権を持っていますが、他のプロジェクトグループにはこの自主権がありません。ここで、あなたの位置を理解することが重要です。製造およびコスト分析エンジニアとのコミュニケーションにより、基板の積層誤差を決定することができます。この場合、基板製造公差を発見する好機です。例えば、ある層が50Ωインピーダンス制御であることを指定した場合、メーカーはどのように測定してこの数値を確保しますか。

他の重要な問題として、予想される製造公差はどのくらいですか。回路基板上で予想される絶縁定数はどのくらいですか。線幅と間隔の許容誤差はどのくらいですか。接地層と信号層の厚さと間隔の許容誤差はどのくらいですか。これらの情報はすべてプリルーティング段階で使用できます。

上記のデータに基づいて、積層を選択することができます。他の回路基板またはバックプレーンに挿入されたPCBのほとんどは厚さ要件があり、多くの回路基板メーカーは製造可能な異なるタイプの層に固定の厚さ要件があり、最終的な積層数を大きく制約することに注意してください。積層の数を定義するためにメーカーと緊密に協力したいかもしれません。インピーダンス制御ツールを使用して、異なる層に目標インピーダンス範囲を生成する必要があります。製造業者が提供する製造許容誤差と隣接配線の影響を考慮しなければなりません。

信号が完全である理想的な場合、すべての高速ノードはインピーダンス制御内層(例えばストリップワイヤ)に配線されなければならないが、実際には、エンジニアは常に外層を使用してすべてまたは一部の高速ノードの配線を行う必要がある。SIを最適化して回路基板をデカップリングするには、接地層/電源層をできるだけペアにして配置する必要があります。接合地層/電源層が1つしかない場合は、我慢するしかありません。電源層がまったくない場合は、定義によってはSIの問題に遭遇する可能性があります。信号のリターンパスが定義されていない前に回路基板の機能をシミュレートしたりシミュレートしたりするのは難しい場合もあります。

4、クロストークとインピーダンス制御

隣接する信号線からの結合は、クロストークをもたらし、信号線のインピーダンスを変化させる。隣接する平行信号線の結合解析は、信号線間または各種信号線間の「安全」または予想される間隔(または平行配線長)を決定する可能性がある。例えば、クロックからデータ信号ノードへのクロストークを100 mV以内に制限しようとしても、信号を引き廻して平行に維持するには、計算やシミュレーションを通じて、任意の配線層上の信号間の最小許容間隔を見つけることができます。また、インピーダンスの重要なノード(またはクロックまたは専用高速メモリアーキテクチャ)が設計に含まれている場合は、所望のインピーダンスを得るために配線を1つのレイヤ(または複数のレイヤ)上に置く必要があります。

5、重要な高速ノード

遅延とタイムラグはクロック配線が考慮しなければならない重要な要素である。タイミング要件が厳しいため、このノードは通常、最適なSI品質を達成するためにエンドデバイスを使用しなければなりません。これらのノードを事前に決定し、信号完全性設計のポインタを調整するために、調整部品の配置と配線に必要な時間を計算します。

6、回路基板の科学技術選択

異なる駆動技術は異なる任務に適している。信号は点対点ですか、それとも点対多タップですか。信号は回路基板から出力されますか、それとも同じ回路基板に残っていますか。許容されるタイムラグと雑音のマージンはどのくらいですか。信号完全性設計の共通基準として、変換速度が遅いほど、信号完全性が良い。50 MHzクロックに500 ps立ち上がり時間を採用するのは理由がない。2-3 nsの振幅制御デバイスの速度は、SIの品質を保証するのに十分に速く、出力同期交換(SSO)や電磁適合(EMC)などの問題を解決するのに役立ちます。

新しいFPGAプログラマブル設計技術またはユーザ定義ASICにおいて、駆動技術の優位性を見つけることができる。これらのカスタムまたはセミカスタムデバイスを採用すると、駆動振幅と速度を選択する余地が大きくなります。設計初期には、FPGAまたはASICの設計時間の要件を満たし、適切な出力選択を決定する必要があります。可能であれば、ピン選択も含まれます。

この設計段階では、ICベンダーから適切なシミュレーションモデルを得る必要があります。SIシミュレーションを効果的に上書きするには、SIシミュレーションプログラムと適切なシミュレーションモデル(IBISモデルの可能性があります)が必要になります。

最後に、プレ配線と配線の段階では、ターゲット層インピーダンス、配線間隔、採用傾向のあるデバイスプロセス、重要なノードトポロジ、および終端計画を含む一連の設計ガイドを作成する必要があります。

7、回路基板の予備配線段階

プレ配線SI計画の基本的なプロセスは、まず入力パラメータ範囲(駆動振幅、インピーダンス、追跡速度)と可能なトポロジ範囲(最小/最大長、短線長など)を定義し、それから可能なシミュレーションの組み合わせを実行し、タイミングとSIシミュレーション結果を分析し、最後に許容できる数値範囲を見つけることです。

続いて、動作範囲をPCB配線の配線制約条件と解釈する。このタイプの「清掃」準備作業は、異なるソフトウェアツールを使用して実行でき、配線プログラムはこのような配線拘束条件を自動的に処理することができます。多くのユーザーにとって、タイミング情報は実際にはSI結果よりも重要であり、相互接続シミュレーションの結果は配線を変更し、信号経路のタイミングを調整することができる。

他の用途では、このプロセスを使用して、システムタイミングポインタに適合しないピンまたはデバイスのレイアウトを決定することができる。この場合、手動配線を必要とするノード、または端子接続を必要としないノードを完全に特定することができます。プログラマブル設計デバイスとASICについては、SI設計を改善したり、離散端子接続デバイスの採用を回避したりするために、出力駆動の選択を調整することもできます。

基板設計

8、回路基板配線後のSIシミュレーション

一般的に、SI設計ガイドラインでは、実際の配線が完了した後にSIやタイミングの問題が発生しないことを保証することは難しい。設計がガイドの指示の下で行われていても、設計を自動的にチェックし続けることができない限り、設計が基準を完全に遵守することは保証できないため、問題が発生することは避けられません。配線後のSIシミュレーション検査では、設計規則を計画的に破ったり変更したりすることができますが、これはコストの考慮や厳しい配線要件の下で必要な作業にすぎません。

現在、SIシミュレーションエンジンを使用すると、高速デジタルPCBまたはマルチボードシステムを完全にシミュレーションでき、SI問題を自動的にマスクし、正確な「ピン対ピン」遅延パラメータを生成することができます。入力信号が十分であれば、シミュレーション結果も同じようによくなります。これにより、デバイスモデルと回路基板の製造パラメータの精度がシミュレーション結果を決定する鍵となる。多くの設計エンジニアが「最小」と「最大」の設計コーナーをシミュレーションし、問題を解決して生産性を調整するために関連情報を採用します。

9、回路基板製造段階

このような措置をとることで、基板のSI設計品質を確保することができ、基板の組み立てが完了した後も、基板を試験プラットフォーム上に置いて、オシロスコープまたはTDR(時間領域反射計)を用いて測定し、実際の基板とシミュレーション予想結果を比較する必要がある。これらの測定データは、次の事前設計調査でより良い(制約の少ない)意思決定を行うために、モデルと製造パラメータを改善するのに役立ちます。

10、モデルの選択

モデル選択に関する記事が多く、静的時系列検証を行っているエンジニアたちは、デバイステーブルからすべてのデータを得ることができるにもかかわらず、モデルを構築するのは難しいことに気づいているかもしれません。SIシミュレーションモデルは逆で、モデルの構築は容易だが、モデルデータは入手しにくい。本質的に、SIモデルデータの唯一の信頼できるソースはICベンダーであり、設計エンジニアとの暗黙の協力が必要です。IBISモデル標準は一貫したデータキャリアを提供しているが、IBISモデルの構築とその品質の保証はコストが高く、ICベンダーの投資には市場ニーズの推進作用が必要であり、回路基板メーカーは唯一の需要家市場である可能性がある。

11、未来の回路基板技術の趨勢

システム内のすべての出力が配線インピーダンスまたは受信回路の負荷に整合するように調整できることを想定して、このようなシステムテストは便利で、SI問題はプログラム設計によって解決することができて、あるいはICの特定のプロセス分布に従って回路基板を調整してSIを要求に達することができて、それによって設計許容差をもっと大きくすることができて、あるいは硬体設定の範囲をもっと広くすることができます。

現在、業界でも注目されているSIデバイステクノロジーの多くは、設計されたエンドコネクタ装置(LVDSなど)と自動プログラマブル設計出力強度制御と動的自動エンドコネクタ機能を含み、これらのテクノロジーを採用した回路基板設計は優れたSI品質を得ることができるが、多くのテクノロジーは標準的なCMOSやTTL論理回路との差が大きすぎて、既存のシミュレーションモデルとの組み合わせがあまりよくない。

このため、EDA社も回路基板設計の競技場に参入しており、設計初期にSI問題を解決するために多くの仕事をしており、将来的にはSI専門家を必要とせずに自動化ツールを利用してSI問題を解決することができるようになっています。現在の技術はまだその水準に達していないが、人々は新しい設計方法を模索しており、「SIとタイミング配線」から基板設計を開始する技術は依然として発展しており、今後数年以内に新しい基板設計技術が誕生する見通しだ。